나노가 뭐길래?…"더 작은 칩에 더 많은 정보 담아라"[반도체 나노 경쟁①]

칩 부피 축소 요구 커…미세공정, 처리 용량·속도↑낮은 수율·천문학적 투자 비용은 한계로 꼽혀

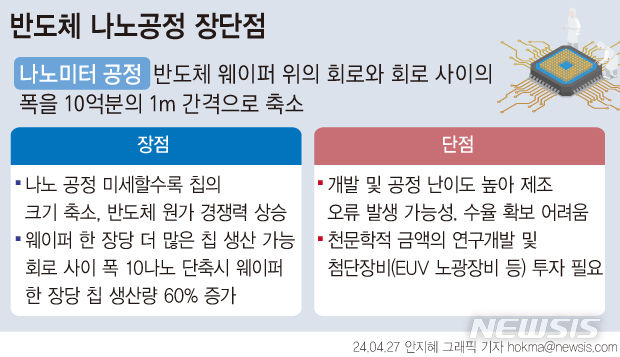

최근 파운드리(반도체 위탁생산) 업계에서 반도체 칩을 더 작게 만들기 위한 '초미세공정' 경쟁이 치열하다. 초미세공정 기술은 이미 '나노미터(㎚)' 수준까지 올라와 있다. 나노는 반도체에 그리는 회로 폭의 단위로, 1나노는 10억 분의 1m이다. 나노 단위 앞의 숫자가 낮을수록 더 미세하다는 뜻이다. 글로벌 파운드리 기업들은 이 같은 나노 기술력을 바탕으로 초미세공정 경쟁에서 우위를 점하기 위해 수천억원에서 수조원의 투자를 이어가고 있다. 27일 업계에 따르면 세계 최대 파운드리 기업인 TSMC는 오는 2026년 하반기 1.6나노 공정 양산을 시작한다. 파운드리 후발주자인 인텔이 올해 말 1.8나노(18A) 공정 양산에 들어간다고 선언한 뒤 TSMC도 새로운 공정 로드맵을 발표했다. 삼성전자도 올해 하반기 3나노 2세대 양산, 내년 2나노 공정 양산에 돌입한다. 이들 기업은 D램, 낸드플래시 등 메모리 반도체를 더 미세한 나노 공정으로 생산하려고 한다. 높은 성능의 반도체를 생산하기 위해선 더 가볍고, 얇고, 작은 '경박단소'의 특성을 최대한 살려야 하기 때문이다. 우선 미세한 나노 공정으로 생산할수록 웨이퍼 한 장당 더 많은 반도체 칩을 만들 수 있다.

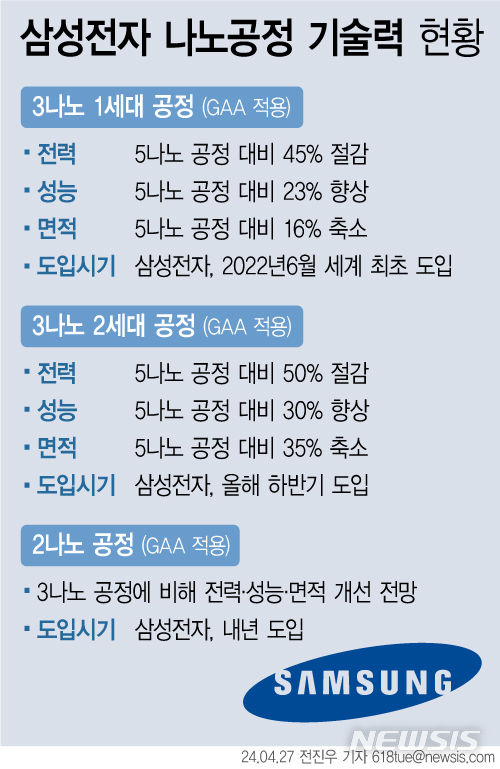

이 같이 회로가 조밀하면 반도체 칩에 더 많은 기억 소자를 배치할 수 있어 데이터 처리 용량은 늘어나고 전송 속도는 빨라진다. 자연스럽게 반도체 칩의 크기와 무게는 줄어든다. 최근 스마트폰과 노트북 등 IT 기기가 얇아지며 '칩 부피 축소'에 대한 고객사들의 요구도 커지는 상황이다. 삼성전자의 경우 지난 2022년 3나노 1세대 공정을 도입해 반도체를 양산하고 있다. 이전 공정인 5나노와 비교하면 성능 23% 향상, 면적 16% 축소, 전력 45% 절감 효과가 있다. 올해 하반기에는 3나노 2세대 공정 양산에 나설 예정이다. 5나노에 비해 성능 30% 향상, 면적 35% 축소, 전력 50% 절감 등 효과를 볼 전망이다. 다만, 초미세공정에서 오류 발생률이 높다는 점은 한계로 꼽힌다. 미세화가 기술적 한계에 다다르면서 공정 난이도가 급격히 높아지고 있기 때문이다. 동시에 결함이 없는 합격품의 비율인 '수율'도 낮아질 수 밖에 없다. 천문학적인 비용이 지속적으로 투입되어야 해 제조기업으로서 부담이 될 수 밖에 없다. 경쟁사들에 뒤처지지 않기 위한 초미세공정 연구개발(R&D)과 고가의 첨단 장비가 필수이기 때문이다. 초미세공정에 필요한 차세대 EUV(극자외선) 장비는 1대당 6000억원이 넘는다. 기존 장비보다 두 배 이상 비싸다. 업계 관계자는 "치열한 파운드리 경쟁으로 기업들의 나노 공정 기술력이 단시간에 급성장했다"며 "한계에 다다른 나노 공정을 어떻게 극복할 지가 업계의 핵심 과제다"고 전했다.

◎공감언론 뉴시스 [email protected] |